5nm工艺、192核心!RISC-V要抢走AMD、Intel的饭碗

|

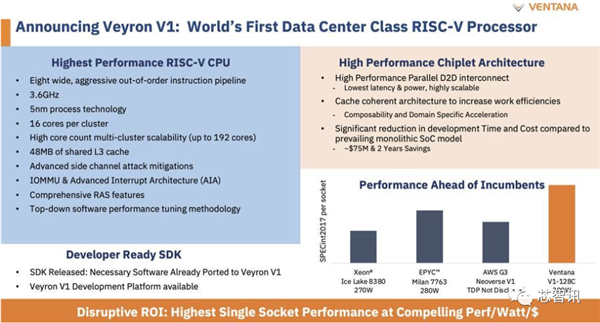

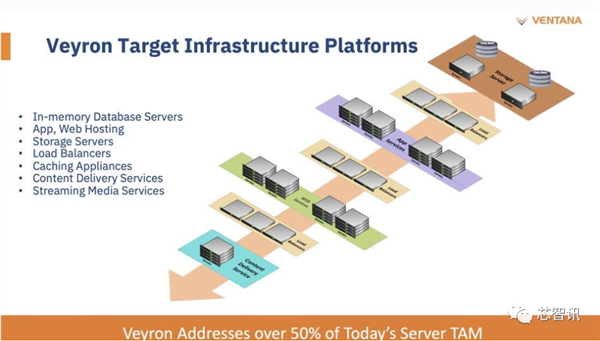

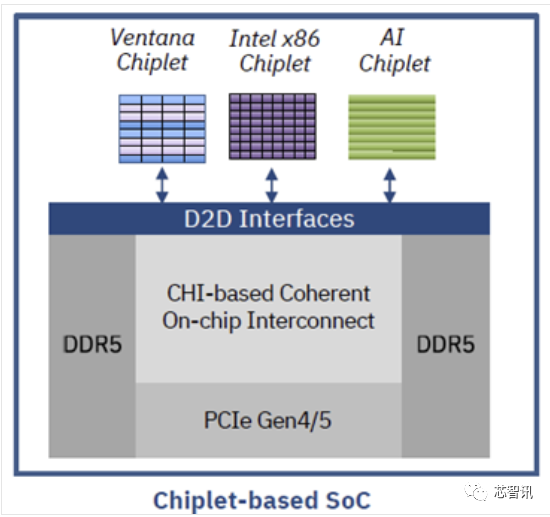

众所周知,目前X86架构处理器统治着PC和服务器市场,Arm架构处理器则统治着移动市场。 近年来大火的RISC-V架构则凭借着于开源、指令精简、可扩展等优势,在注重能效比的物联网领域大受追捧。 但是,这并不意味着RISC-V无法进入更高性能要求的PC和服务器市场。 继不久前国产RISC-V芯片厂商赛昉科技推出了全球首款面向PC应用的高性能RISC-V芯片——昉·惊鸿8100之后,据福布斯网站12月12日报道,芯片初创企业Ventana Microsystems公司在RISC-V峰会上发布了全球首款面向服务器的CPU——Veyron V1。 据介绍,Veyron V1采用先进的5nm制程工艺,基于Ventana自研的高性能RISC-V内核,8流水线设计,支持乱序执行,主频高达3.6GHz,每个集群最多16个内核,多集群最多可扩展至192核,拥有48MB共享三级缓存。 它拥有高级侧信道攻击缓解措施、IOMMU和高级中断架构(AIA),支持全面的RAS功能、自上而下的软件性能调整方法,可以满足数据中心的各种需求。 据Ventana披露的数据显示,在SPECint 2017测试中,128核心版本的Veyron V1在300W功耗下,大幅性能领先于64核的AMD EPYC Milan 7763(280W),并且达到了AWS Graviton G3(Neoverse v1)、Intel Xeon Ice Lake 8380(270W)的两倍。 由于目前RISC-V软件生态系统仍不成熟,因此Veyron V1还并不能算是一款通用型的服务器CPU。 不过,Vnetana认为,其解决方案将能够满足数据中心CPU市场50%的需求,比如内存数据库服务、APP应用及虚拟主机服务、存储服务器、负载平衡、缓存设备、内容交付服务、流媒体服务等。 值得一提的是,Veyron V1采用了类似AMD EPYC处理器那样的Chiplet设计。 Vnetana表示,Veyron V1支持高性能并行Die to Die互连,拥有低延迟和低功耗,高度可扩展等特性。 Ventana表示,其I/O总线延迟可以低至7ns,其缓存一致性架构也可提高工作效率,Chiplet设计也使得其更具可组合性。 对于Die to Die 互连,Ventana 计划同时支持 Intel、AMD、NVIDIA、Arm 等支持的 BoW(线束)和通用 Chiplet Interconnect Express (UCIe) 标准。 此外,Ventana 还从十几个 IP/chiplet 合作伙伴那里获得了支持,为基于小芯片的解决方案提供交钥匙解决方案,以及强大的 SDK,包括固件、BIOS、操作系统、存储和网络参考应用程序以及 BMC。 因此,Vnetana允许客户从他那里购买其CPU、I/O模块,可以跟客户自己的加速器IP整合形成自己的芯片。 Vnetana表示,客户选择Ventana的CPU、I/O模块来设计自己的SoC可以缩短两年的开发时间,并节省7500万美元的研发费用。 按照计划,Veyron V1已经流片成功,预计将会在2023年年中正式推出,并在2023年下半年成功部署于数据中心基础设施。 根据官方资料介绍,Vnetana公司成立于2018年,创始团队包括多位行业资深人士,拥有超过20年的平均经验,曾在所有主要的ISA上工作(包括x86,Arm,Power,MIPS和SPARC),并在交付数据中心级处理器方面有着良好的记录。今年该公司还获得了5500万美元的新一轮融资。 |